XBee Sockets and FTDI Interface Headers

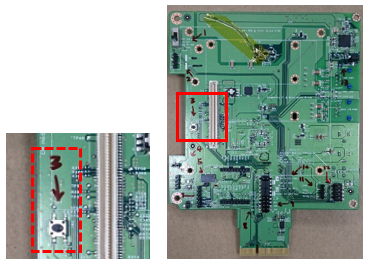

XBee socket headers are comprised of two 2.0 mm pitch headers (J10 and J11). The pin definition is shown in the figures below.

Figure 14: XBee Socket (J10/J11 2*10P 2.0mm)

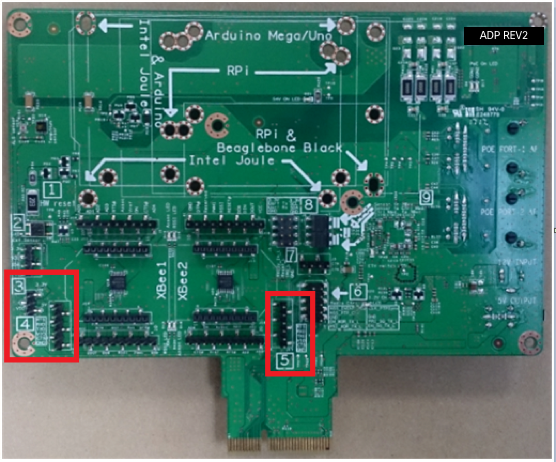

Figure 15: XBee Socket Location

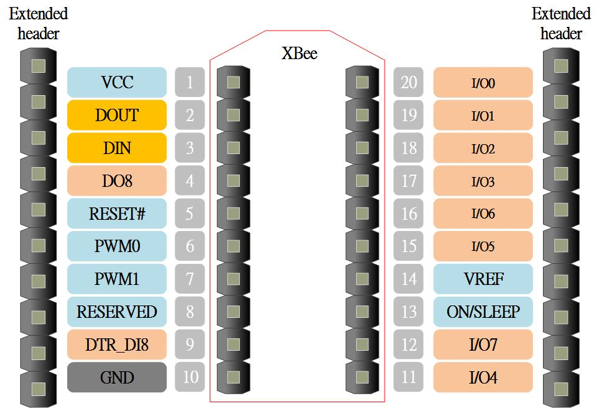

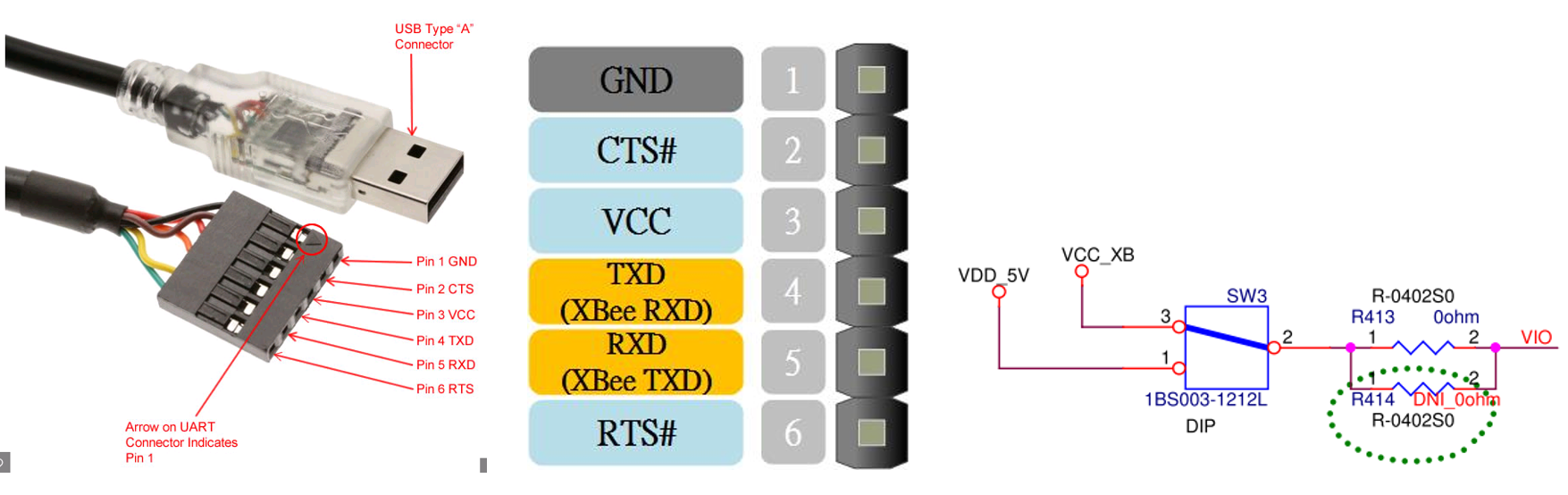

The signal control pins are a 6-pin header (J12), as shown in this figure below. There is a switch slide (SW3) to select between 3.3V or 5V for the power level of the control pin. The location of the switch slide is No. 5 as shown in this figure below.

Figure 16: Signal Control Header and Power Switch (J12 1*6P 2.54mm)

Figure 17: Signal Control Header and Voltage Header Location (No. 3, 4, 5)

The 6-pin header is used to program and configure the XBee radio. It is intended to be used in conjunction with a standard FTDI-USB serial adapter. It is not connected anywhere else on the HDK.

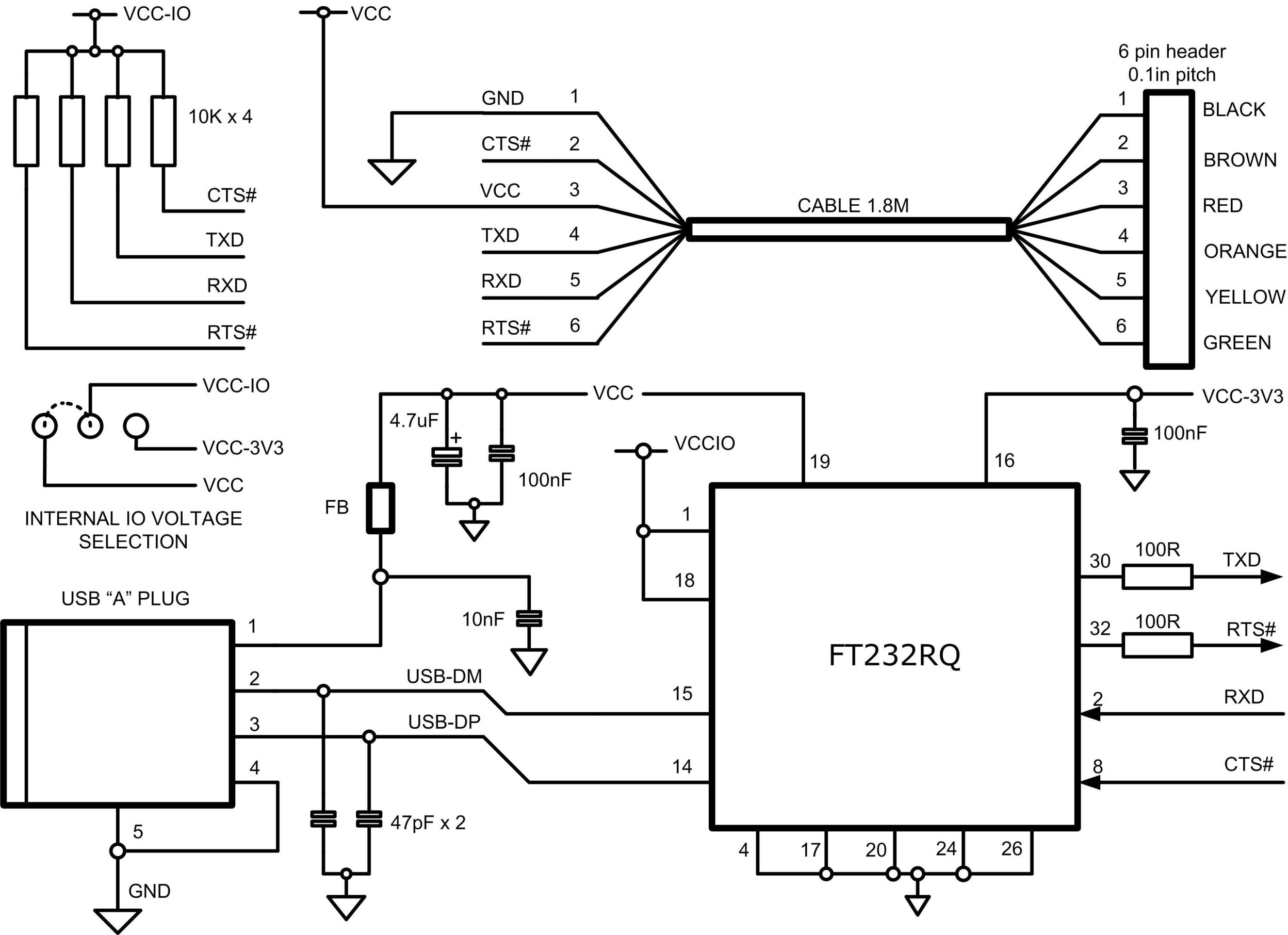

A typical FTDI serial adapter cable circuit implementation is shown below.

Figure 18: FTDI Serial Adapter Cable Circuit

802.3af/at Power Selection Header

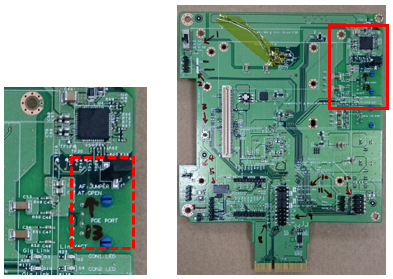

The header J8 selects between 802.3af or 802.3at PSE class output power. The header location is No. 13.

NOTE: PSE output power is limited by available AP3800 host power. AP3800 has a maximum 18W total budget for the HDK; approximately 14W total is available for PD devices when no other hardware is attached to the HDK power supply. The AP3800 will shut down power to the HDK via efuse if the 18W limit is exceeded

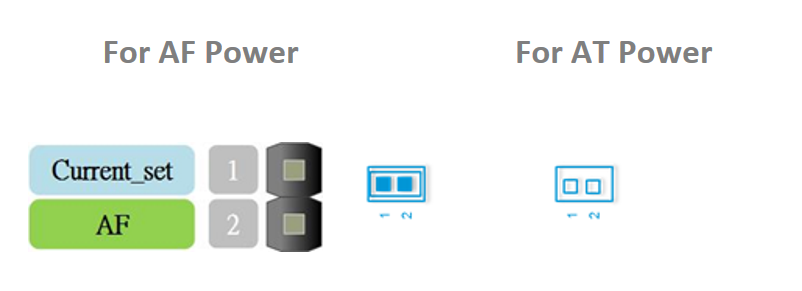

To set the PSE output power:

- (Default Setting) For 802.3af PSE output power, providing 54V 13.4W/23W output, place jumper across Pin-1 and Pin-2.

- For 802.3at PSE output power, 54V 30W output, remove the jumper from Pin-1 and Pin-2.

Figure 19: AF/AT Selection Header (J8 1*2P 2.54mm)

Figure 20: AF/AT Selection Header at location No. 13

I2C selection and UART

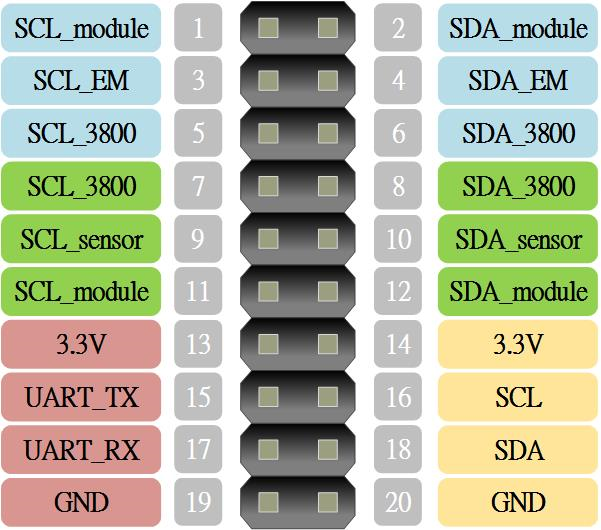

The J4 20-pin header contains I2C selection and UART control pins.

The I2C scheme and address are shown in the table and figures below. The locations are from No. 8 to No. 10.

| Purpose | Put Jumpers Coupling these Pins | Location |

|---|---|---|

| EM module to AP3800 | pins 3 and 5, pins 4 and 6. This is the default setting. | No. 10 |

| Sensor to AP3800 | pins 7 and 9, pins 8 and 10. This is the default setting. | No. 10 |

| EM module and HDK Sensor to 3rd party control module | pins 1 and 3, pins 2 and 4. Or, pins 9 and 11, pins 10 and 12 | No. 10 |

| I2C control pin for 3rd party control module | pin 14 and 16, pins 18 and 20 | No. 9 |

| UART signal is connected to AP38xx for 3rd party control module | pins 13 and 15, pins 17 and 19 | No. 8 |

Figure 21: I2C and UART header (J4 2*10P 2.54mm)

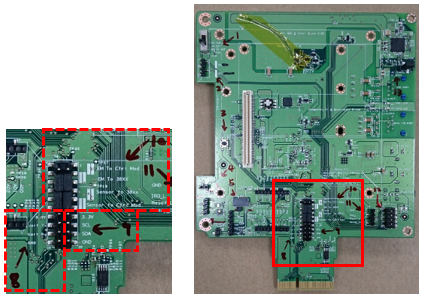

Figure 22: I2C and UART header (No. 8, 9, 10)

Figure 23: I2C and UART scheme

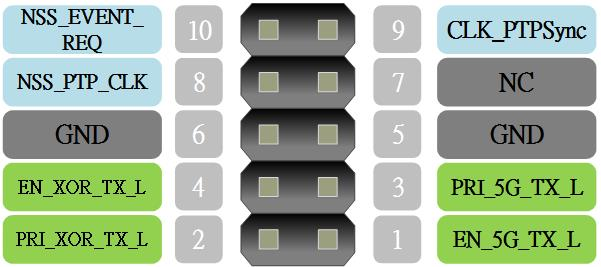

Coexistence/PTP Header

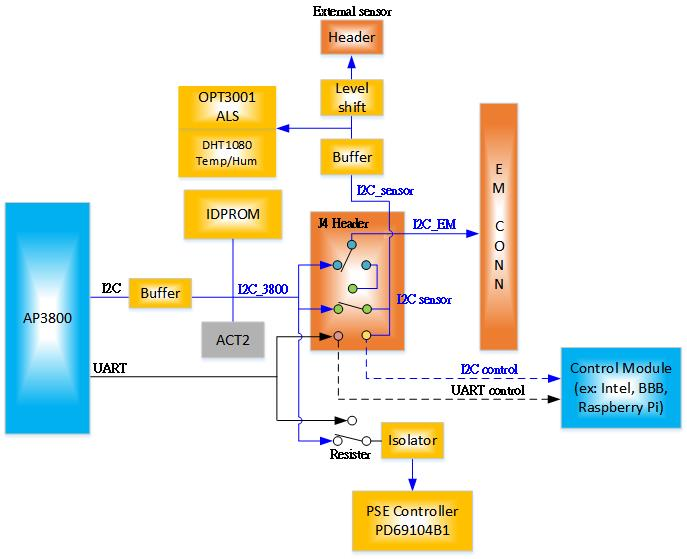

J2 header provides radio coexistence and Precision Time Protocol interface to the AP3800. The location is No. 12.

External radios should utlitize the coexistence lines to avoid coexistence issues with the AP3800 2.4G or 5GHz radios.

Figure 24: Radio Control Header (J2 2*5P 2.54mm)

Figure 25: Radio Control Header location (No. 12)

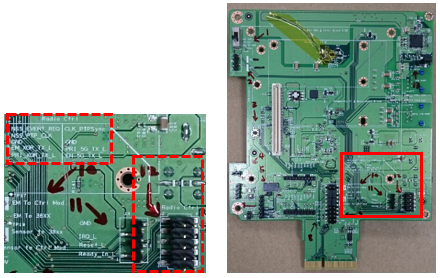

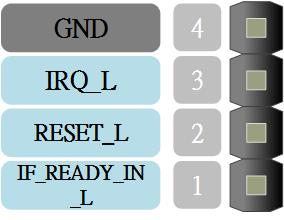

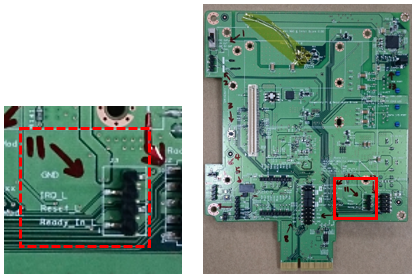

Reset / Interrupt Header

The J3 header contains the system reset/interrupt control of the PSE chip and Ethernet switch pin, as shown in the figure below. The location is No. 11.

Figure 26: Reset/Interrupt header (J3 1*4P 2.54mm)

Figure 27: Reset/Interrupt header location (No. 11)

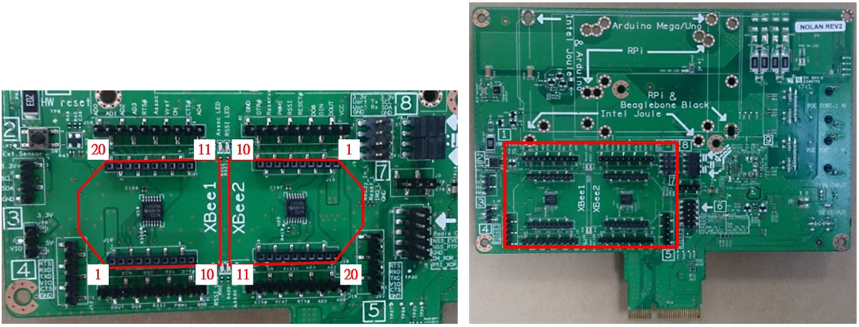

Hardware Reset Button

A reset button physically asserts the HDK's switch, PSE controller, and IDPROM reset lines. It does not reset the AP3800. Any soft-written configs from the AP3800 will be lost. The reset line asserts for a minimum of 240mS after the reset button is released.

The location is No. 3, as shown in the figure below.

Figure 28: Hardware Reset Button Location (No. 3)